# Pulse Control LSI PCL6115/6125/6145

## **User's Manual**

**NPM** Nippon Pulse Motor Co., Ltd.

#### [Preface]

Thank you for considering our pulse control LSI, the "PCL6100 series."

Before using the product, please read this manual to become familiar with it.

Please note that the section "Handling Precautions", which includes the details of installing these ICs, is shown at the end of this manual.

#### [Cautions]

(1) Copying all or any part of this manual without written approval is prohibited by copyright laws.

- (2) The specifications of these LSIs may be changed to improve performance or quality without prior notice.

- (3) Although this manual was produced with the utmost care, if you find any points that are unclear, wrong, or have inadequate descriptions, please let us know.

- (4) We are not responsible for any results that may occur from using these LSIs, regardless of item (3) above.

- Explanation of the description in this manual

- 1. The suffix "x", "y", "z", and "u" of terminal names and bit names refer to X-axis, Y-axis, Z-axis, and U-axis, respectively.

- 2. Over-lines above negative logic terminal names (ex. RST) are not used in this manual. Please refer to the "<u>3-3. Terminal List</u>" for the logic.

- 3. When describing the bits in registers, "n" refers to a bit position. "0" refers to a bit position and it is prohibited to be written to any other than "0". This bit always returns "0" when it is read.

- 4. The specific bit in a status or in a register is shown as follows:"Status name.Bit name" or "Register name.Bit name" (e.g. RMD.MSDE)

- 5. If there is a description of time in this manual, it shows the value at "reference clock frequency of 19.6608 MHz" unless otherwise noted.

- 6. Signal status "ON" is shown by "H level" or "1" for the positive logic while "L level" or "0" for the negative logic in terms of "ON/OFF" of the signal status.

- As for the suffix attached to numbers, "b" indicates a binary number and "h" indicates a hexadecimal number. Suffixes are not attached to decimal numbers.

Some binary numbers or hexadecimal numbers may not be suffixed when the values are the same in some charts or the decimal numbers.

## **INDEX**

| 1. Outline and Features                                                | 1  |

|------------------------------------------------------------------------|----|

| 1-1. Outline                                                           | 1  |

| 1-2. Features                                                          | 1  |

| 2. Specification                                                       | 6  |

| 3. Hardware Description                                                | 7  |

| 3-1. External dimensions                                               | 7  |

| 3-2. Terminal Assignment Diagrams                                      | 13 |

| 3-3. Terminal List                                                     | 16 |

| 3-3-1. PCL6115                                                         | 16 |

| 3-3-2. PCL6125                                                         | 21 |

| 3-3-3. PCL6145                                                         |    |

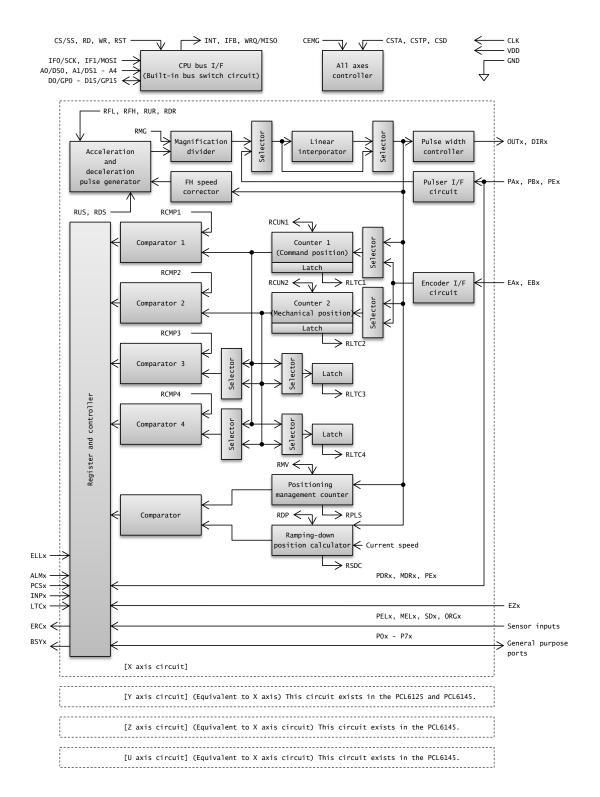

| 3-4. Block Diagram                                                     | 40 |

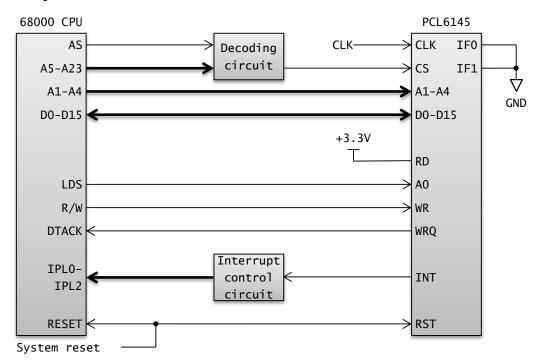

| 3-5. CPU bus I/F                                                       | 41 |

| 3-5-1. Parallel bus I/F                                                | 41 |

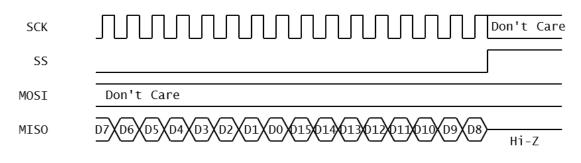

| 3-5-2. Serial Bus I/F                                                  | 44 |

| 4. Software                                                            | 45 |

| 4-1. CPU access                                                        | 45 |

| 4-1-1. Parallel communication                                          | 45 |

| 4-1-2. Serial communication                                            |    |

| 4-2. Status                                                            | 64 |

| 4-2-1. Main status (MSTS)                                              | 64 |

| 4-2-2. Sub status (SSTS) and general-purpose input/output ports (IOP). | 67 |

| 4-2-3. Extention status (RSTS)                                         | 67 |

| 4-3. Commands                                                          |    |

| 4-3-1. Operation commands                                              |    |

| 4-3-2. General-purpose output bit control commands                     | 70 |

| 4-3-3. Control commands                                                |    |

| 4-3-4. Register control command                                        | 73 |

| 4-4. Registers (Pre-registers)                                         | 75 |

| 4-4-1. Pre-register                                                    | 75 |

| 4-4-2. Speed control registers                                         |    |

| 4-4-3. Position control register                                       |    |

| 4-4-4. Environment setting registers                                   |    |

| 4-4-5. Count register                                                  |    |

| 4-4-6. Interrupt register                                              |    |

| 4-4-7. Status indicating register                                      |    |

|                                                                        |    |

| 5. Operation Mode                                                      |    |

| 5-1. Command control                                               | 107 |

|--------------------------------------------------------------------|-----|

| 5-1-1. Positive direction continuous opertaion mode (MOD : 00h)    |     |

| 5-1-2. Negative direction continuous operation mode (MOD : 08h)    |     |

| 5-2. Positioning operation mode                                    |     |

| 5-2-1. Incremental movement operation mode (MOD: 41h)              |     |

| 5-2-2. Timer operation mode (MOD: 47h)                             |     |

| 5-3. Manual pulser operation                                       |     |

| 5-3-1. Continuous movement operation mode (MOD: 01h)               | 112 |

| 5-3-2. Incremental movement operation mode (MOD: 51h)              | 112 |

| 5-4. Switch operation                                              | 113 |

| 5-4-1. Continuous movement operation mode (MOD: 02h)               | 114 |

| 5-4-2. Incremental movement operation mode (MOD: 56h)              | 115 |

| 5-5. Origin return operation                                       | 116 |

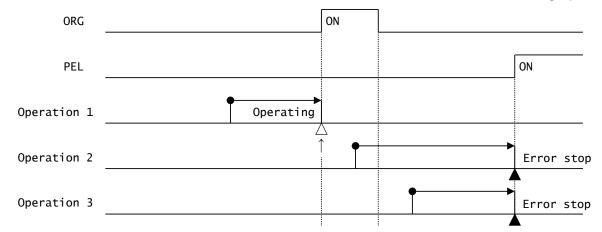

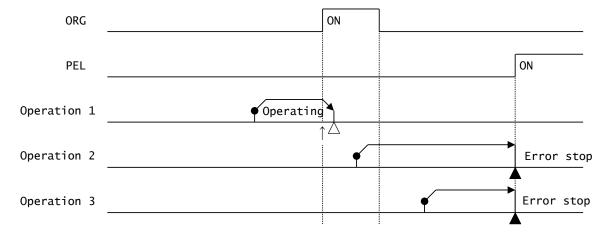

| 5-5-1. Origin return operation 0 (RENV2.ORM = 0)                   | 119 |

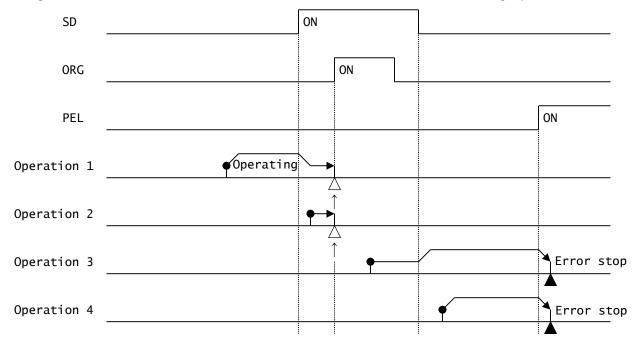

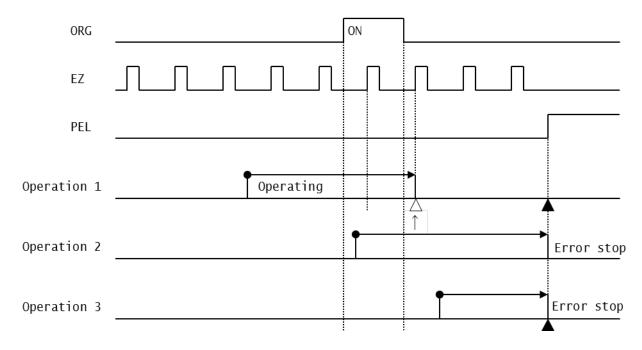

| 5-5-2. Origin return operation 1 (RENV2. ORM = 1)                  | 121 |

| 5-6. Linear interpolation operation mode                           | 125 |

| 5-6-1. Continuous operation mode (MOD:62h)                         | 126 |

| 5-6-2. Incremental movement operation mode (MOD : 63h)             | 128 |

| 6. Speed patterns                                                  | 129 |

| 6-1. Speed pattern list                                            | 129 |

| 6-2. Speed pattern settings                                        | 130 |

| 6-2-1. Speed control register calculations                         | 131 |

| 6-2-2. Speed pattern setting example                               | 135 |

| 6-3. Manual FH correction calculation                              | 137 |

| 6-3-1. Linear acceleration/deceleration speed                      | 138 |

| 6-3-2. Complete S-curve acceleration/deceleration                  | 138 |

| 6-3-3. Partial S-curve acceleration/deceleration                   | 138 |

| 6-4. Target speed override                                         | 141 |

| 7. Description of the Functions                                    | 143 |

| 7-1. Reset                                                         | 143 |

| 7-2. Target position override                                      | 144 |

| 7-2-1. Target position override 1 (RMV register)                   | 144 |

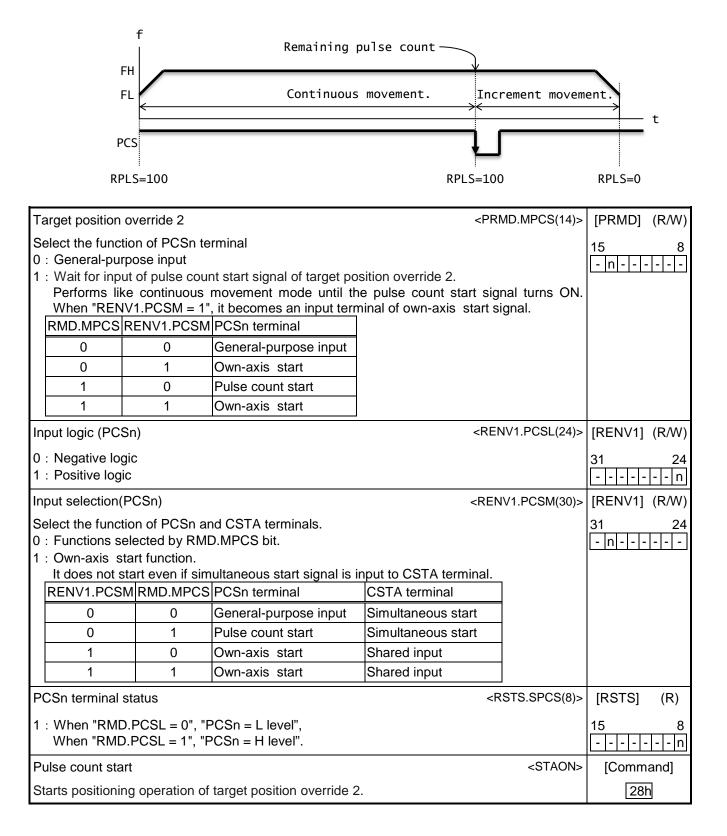

| 7-2-2. Target position override 2 (PCSn)                           | 146 |

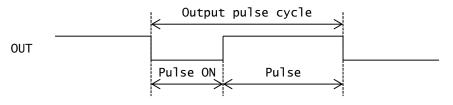

| 7-3. Output pulse control                                          | 147 |

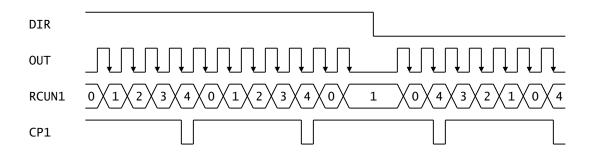

| 7-3-1. Output pulse mode (OUTn, DIRn)                              | 147 |

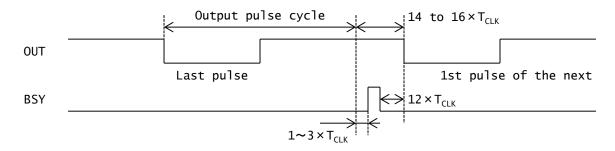

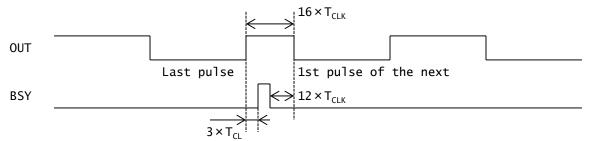

| 7-3-2. Output pulse length and operation complete timing           | 148 |

| 7-4. Mechanical external input control                             | 149 |

| 7-4-1. End limit signal (PELn, MELn)                               | 149 |

| 7-4-2. Slow–down signal (SDn)                                      | 151 |

| 7-4-3. Origin position signal (ORGn), encoder Z-phase signal (EZn) | 154 |

| 7-5. Servomotor I/F                           | 156 |

|-----------------------------------------------|-----|

| 7-5-1. Positioning complete signal (INPn)     | 156 |

| 7-5-2. Deviation counter clear signal (ERCn)  | 157 |

| 7-5-3. Alarm signals (ALMn)                   | 159 |

| 7-6. Simultaneous start                       | 160 |

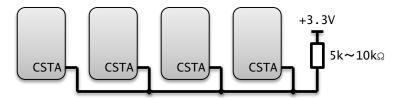

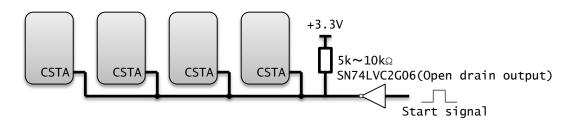

| 7-6-1. Simultaneous start signal (CSTA)       | 160 |

| 7-6-2. Own-aixs start signal (PCSn)           | 162 |

| 7-7. Simultaneous deceleration                | 163 |

| 7-7-1. Simultaneous deceleration signal (CSD) | 163 |

| 7-8. Simultaneous stop                        | 164 |

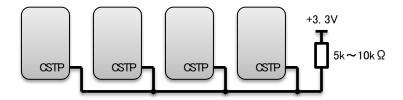

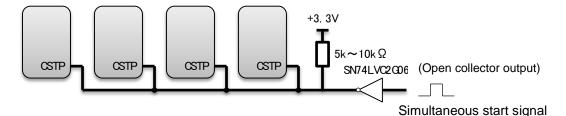

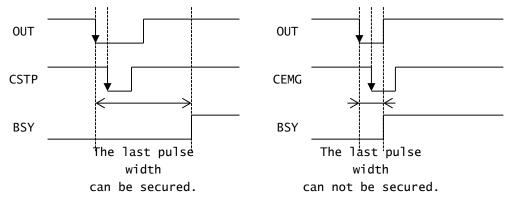

| 7-8-1. Simultaneous stop signal (CSTP)        | 164 |

| 7-9. Emergency stop                           | 166 |

| 7-9-1. Emergency stop signal (CEMG)           | 166 |

| 7-10. Counters                                | 167 |

| 7-10-1. Counter type and input specification  | 167 |

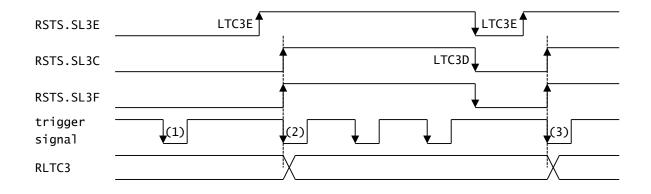

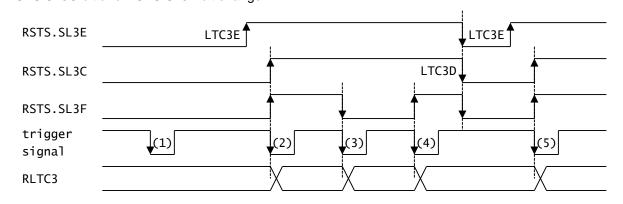

| 7-10-2. Latch and clear (LTCn)                | 169 |

| 7-10-3. Operation stop and input stop         | 176 |

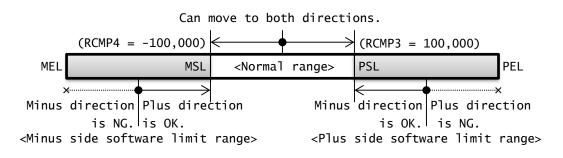

| 7-11. Comparators                             | 177 |

| 7-11-1. Comparator types and the functions    | 177 |

| 7-11-2. Ring count function                   | 179 |

| 7-11-3. Software limit function               |     |

| 7-12. Synchronous starting                    |     |

| 7-12-1. Start by stopping the target axis     |     |

| 7-12-2. Start by internal synchronous signal  |     |

| 7-13. Interrupt (INT) function                | 185 |

| 7-13-1. Error interrupt factors               |     |

| 7-13-2. Event interrupt factors               |     |

| 7-14. ID Monitor                              |     |

| 8. Electrical Characteristics                 |     |

| 8-1. Absolute maximum ratings                 |     |

| 8-2. Recommended operating conditions         |     |

| 8-3. DC characteristics                       |     |

| 8-3-1. PCL6115                                |     |

| 8-3-2. PCL6125                                | 190 |

| 8-3-3. PCL6145                                | 190 |

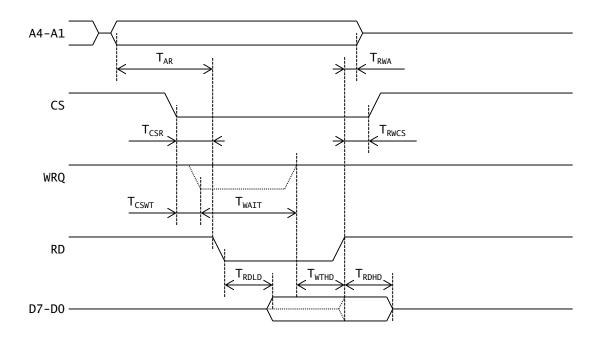

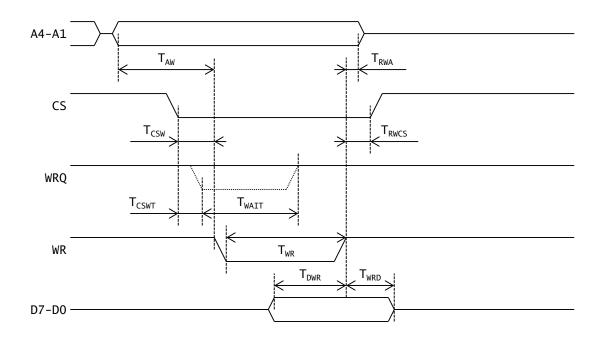

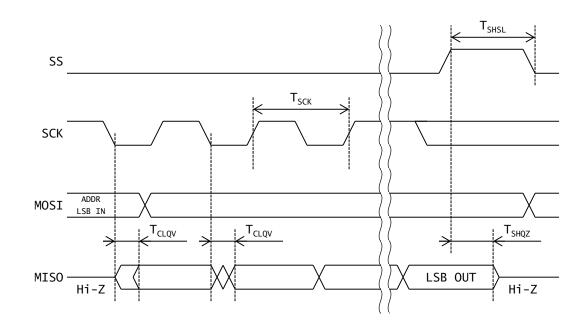

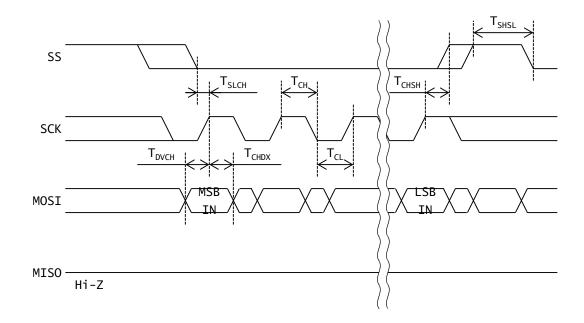

| 8-4. AC characteristics                       | 191 |

| 8-4-1. Reference Clock                        | 191 |

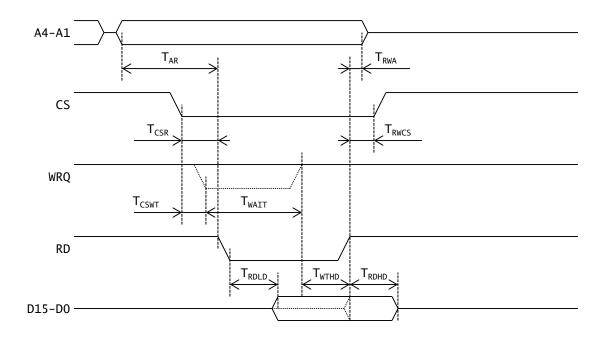

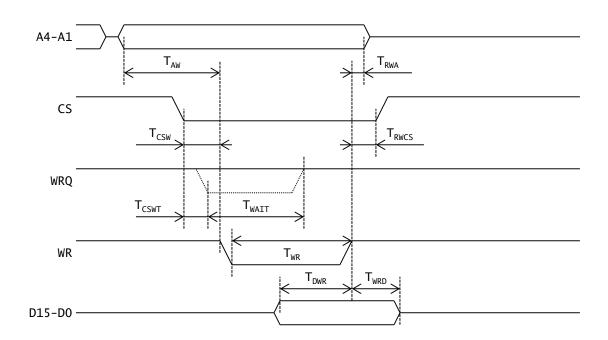

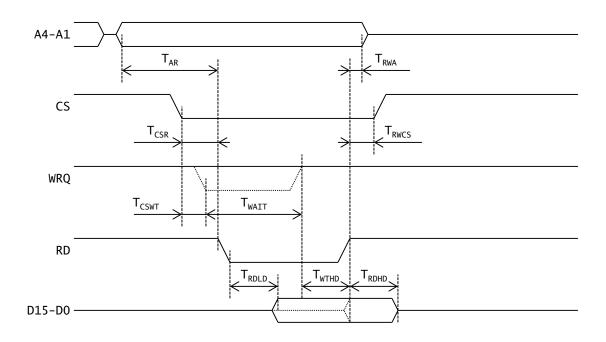

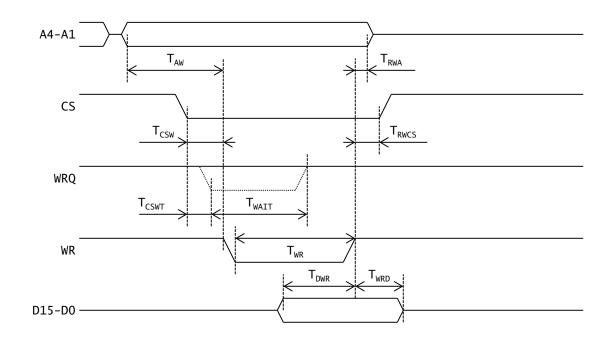

| 8-4-2. 16-bit I/F-1) 68000, etc               | 192 |

| 8-4-3. 16-bit I/F-2 (H8, etc.)                | 194 |

| 8-4-4. 16-bit I/F-3 (8086, etc.)              | 197 |

| 8-4-5. 8-bit I/F-2 (Z80, etc.)                                                 |

|--------------------------------------------------------------------------------|

| 8-4-6. Serial I/F203                                                           |

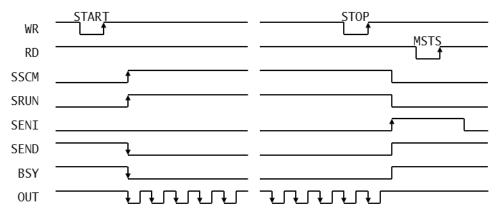

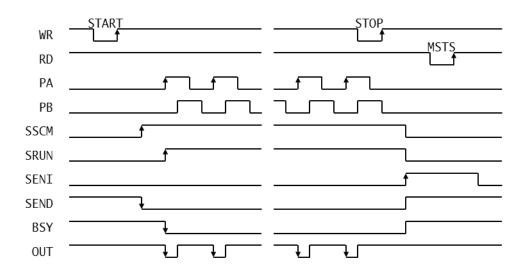

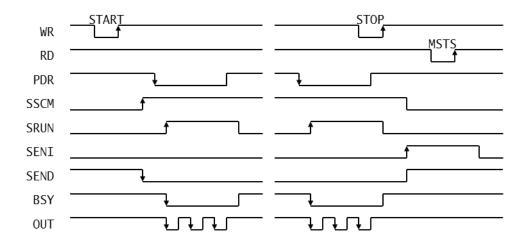

| 8-5. Operation timing (common for all axes)205                                 |

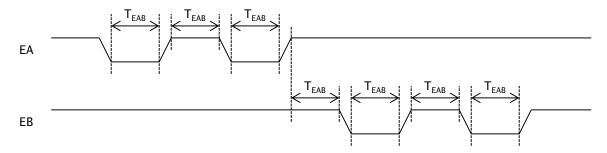

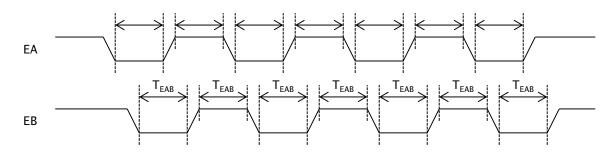

| 8-5-1. When the EA, EB inputs are in the 2-pulse mode206                       |

| 8-5-2. When the EA, EB inputs are in the 90-degree phase difference mode       |

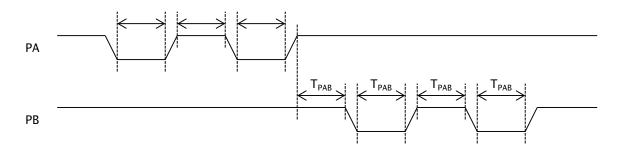

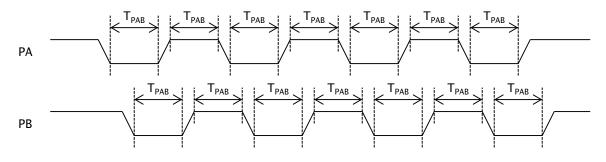

| 8-5-3. When the PA, PB inputs are in the 2-pulse mode206                       |

| 8-5-4. When the PA, PB inputs are in the 90-degree phase difference mode       |

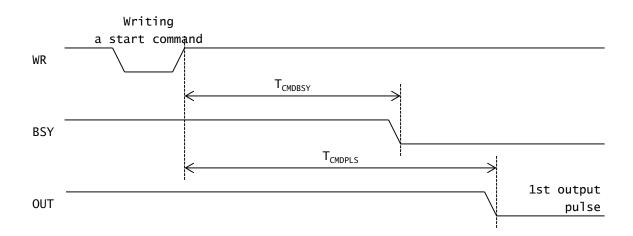

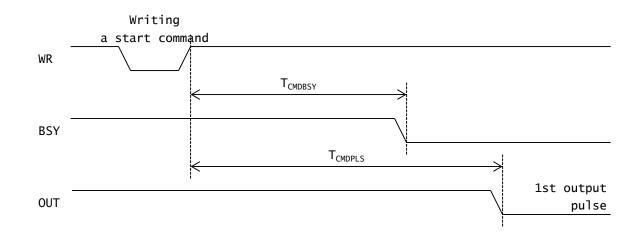

| 8-5-5. Timing for the command start (when I/M = H level, and B/W = H level)207 |

| 8-5-6. Simultaneous start timing207                                            |

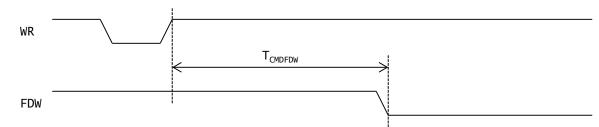

| 8-5-7. Deceleration start timing triggered by a command207                     |

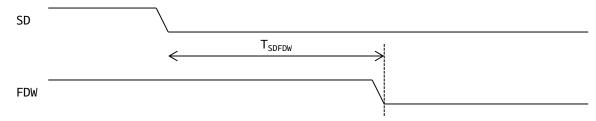

| 8-5-8. Deceleration start timing triggered by the SD input207                  |

| 8-5-9. Stop timing by a command208                                             |

| 8-5-10. Stop timing by normal stop208                                          |

| 8-5-11. Stop timing by error                                                   |

| 9. Handling Precautions                                                        |

| 9-1. Design precautions210                                                     |

| 9-2. Precautions for transporting and storing LSIs210                          |

| 9-3. Precautions for handling environment210                                   |

| 9-4. Precautions for installation                                              |

#### 1. Outline and Features

#### 1-1. Outline

The PCL6115, PCL6125, and PCL6145 are CMOS based Pulse Control LSIs.

They are designed to output high-speed pulses in order to drive stepper motors and servomotors by various commands from CPU.

They provide various types of controls including constant speed, linear acceleration/deceleration, S-curve acceleration/deceleration, continuous move, relative move, and origin return operation, etc.

The number of control axes is; one for the PCL6115, two for the PCL6125, and four for the PCL6145.

The operation status of LSI can be monitored from the CPU, and the LSI can output interrupt signals per a variety of conditions.

They also incorporate functions for servomotor driver control, such as input terminal for positioning completion signal and output terminal for deviation counter clear signal.

In addition, they are equipped with servomotor driver control features.

These functions can be controlled with simple commands. Moreover, the intelligent design with the LSI will reduce the burden over the CPU units regarding motor controls.

#### 1-2. Features

#### ♦ 3.3 V single voltage power supply

These LSIs operate by a single 3.3 V power supply.

The output signal level range is 0 V to 3.3 V. The input signal level range is 0 V to 3.3 V or 0 V to 5 V.

#### Super high-speed pulse train output

Up to 9.8 Mpps of command pulses can be output when using the 19.6608 MHz (standard) reference clock frequency, Up to 15 M pps output is available to output when using the 30 MHz (maximum) reference clock.

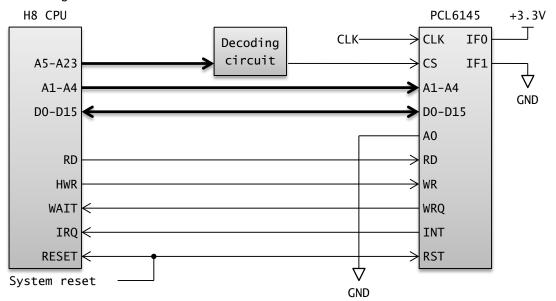

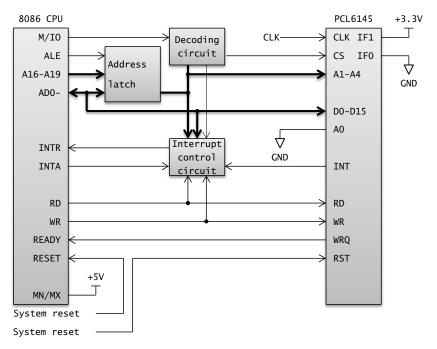

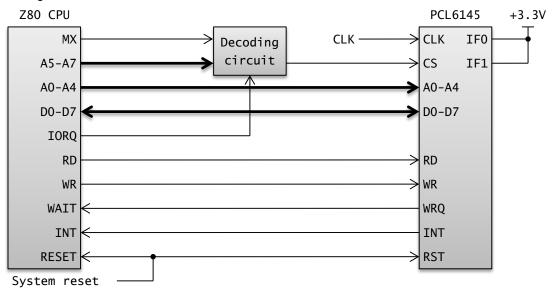

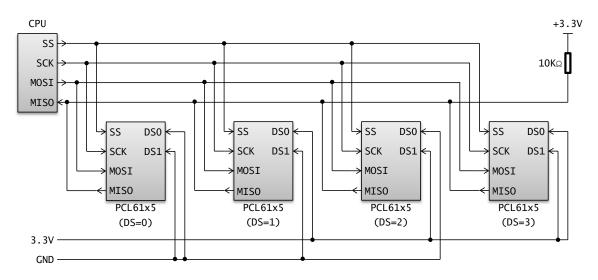

#### ♦ CPU bus I/F

These LSIs have built-in parallel bus I/F (8-bit: 1 type, 16-bit: 3 types) and a serial bus I/F (4-wire synchronous type: 1 type), so that they can be connected to a wide variety of CPUs.

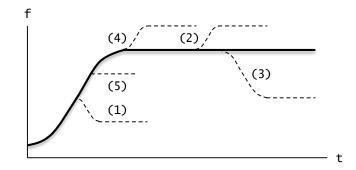

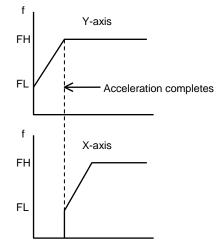

#### Acceleration/Deceleration control

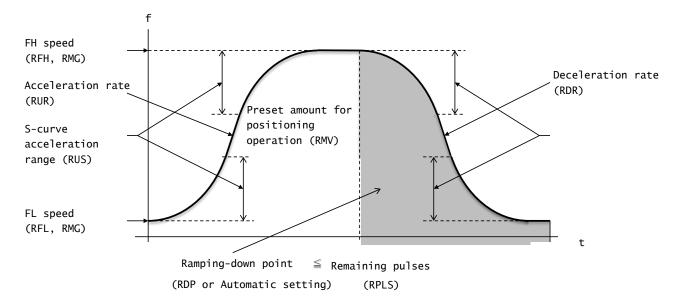

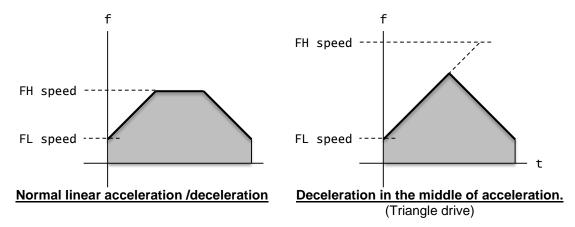

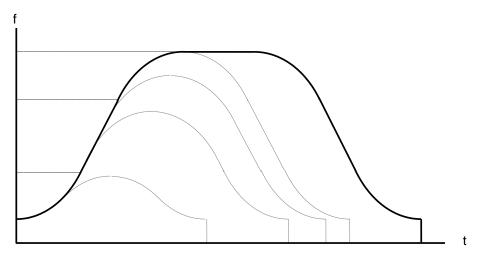

Linear acceleration/deceleration or S-curve acceleration/deceleration is selectable. Linear acceleration/deceleration can be inserted in the middle of an S-curve acceleration/deceleration curve by setting S-curve range.

The S-curve range can be set differently between acceleration and deceleration.

If the S-curve range is extremely short, such as setting the S-curve range to 1 pps or less, it will appear to be linear acceleration/deceleration. Therefore, you can perform S-curve deceleration after linear acceleration or linear-deceleration after S-curve acceleration.X-axis

#### Linear interpolation

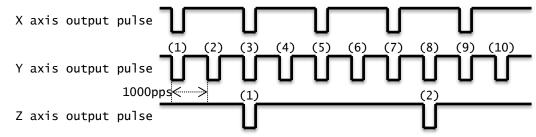

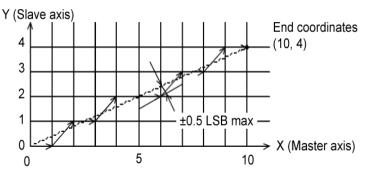

These LSIs can perform linear interpolation (= synchronized operation) for any number of axes.

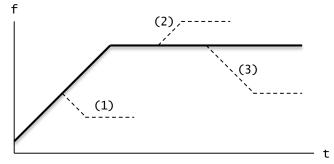

#### Target speed override

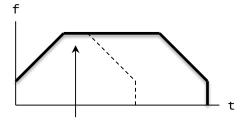

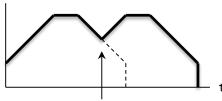

Target speed (operation speed) can be changed during an operation of positioning control incremental movement mode. Target speed (operation speed) and the speed pattern can be changed during an operation of command control continuous movement mode.

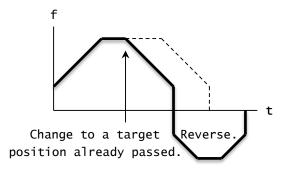

#### Target position override 1) and 2)

- 1. Target position (feeding amount) can be changed during an operation of positioning control incremental movement mode. If the motor position has already exceeded the new target position, it will decelerate and stop (immediate stop for a constant speed start), and then move in the reverse direction.

- Operation starts in the same way as the continuous mode before the input of pulse count start signal. Once the signal is input, LSI will start a positioning control and can stop by outputting the specified number of pulses.

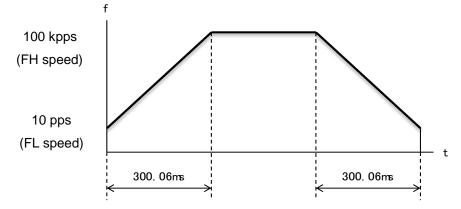

#### Triangle drive elimination (Automatic FH correction function)

In a positioning control incremental operation, deceleration may start during acceleration if the operation speed (FH speed) is too high for the feeding amount. It is called a triangular drive and it may cause vibration or out-of-stop step issue. To avoid the issue, operation speed can automatically be reduced and triangular drive can be avoided.

#### Pre-register

The LSI has a built-in pre-register (one stage) for storing the operation data. During operation, data for the next operation is set from the CPU, and the data can be executed continuously immediately after the current operation completes.

#### Counter circuits

The following two counters are available separately for each axis.

| Counter           | Purpose of use                                 | Count Input                               |

|-------------------|------------------------------------------------|-------------------------------------------|

| COUNTER 1 (RCUN1) | 32-bit counter for command position control    | Command pulse or Encoder signal (EAn/EBn) |

| COUNTER 2 (RCUN2) | 32-bit counter for mechanical position control | Encoder signal (EAn/EBn) or Command pulse |

Either counter can be cleared by writing a command. Also the counter data can be latched by writing a command, LTC signal, or ORG signal, etc.

They can also be cleared immediately after latching values.

#### Comparators

There are 4 comparator circuits for each axis. They can be used to compare target values and internal counter values. Comparator 1 can be compared with COUNTER 1 and Comparator 2 can be compared with COUNTER 2. Comparator 3 and 4 are for software limit function only.

#### Simultaneous start function

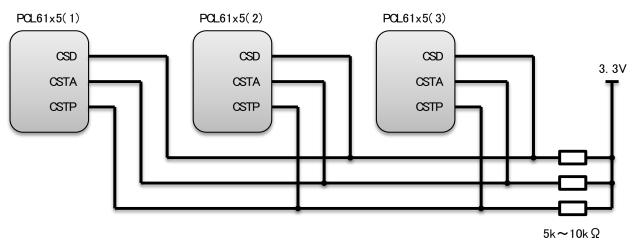

Multiple axes controlled by one LSI or multiple axes controlled by multiple LSIs can be started simultaneously by a command or a simultaneous start signal.

#### Simultaneous stop function

Multiple axes controlled by one LSI or multiple axes controlled by multiple LSIs can be stopped simultaneously by an error stop of other axis.

#### Manual pulser input function

By applying signals with a manual pulser, a motor can be driven directly.

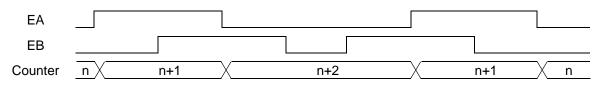

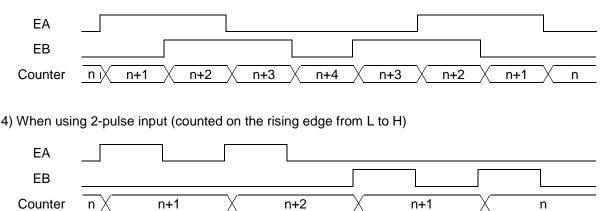

Input signals are 90 degree phase difference signal (1x, 2x, or 4x) or 2 pulse signal (up and down pulse signals). It can be stopped within the range of end limit signals or software limit signals on the plus side or the minus side. After being stopped by the end limit signal or software limit range, you can operate only in the opposite direction by reversing the manual pulser signal.

You can conduct continuous movements by inputting a manual pulser signal, and also conduct incremental movements to stop at the target position.

#### Direct input of external operation switch

A motor can be directly driven by inputting an external operation switch signal.

The input terminal is shared with the manual pulser terminal. These switches turn a motor forward (+ direction) and backward (– direction) in accordance with the external switch signal. It can conduct a continuous movement that a motor moves continuously only while the external switch signal is ON or and can conduct a relative movement that a motor stops at the target position.

#### Operation mode

The basic operations are continuous operations, incremental operations, origin returns, and linear interpolations.

By setting bits for optional operation modes, a variety of operations are available.

<Examples of operation modes>

- 1) Continuous move by a command control

- 2) Continuous move and an incremental operation using a manual pulser control

- 3) Continuous move and incremental operation using an external switch control

- 4) Origin positon return by an origin return operation.

- 5) Positioning operation using incremental operation

- 6) Hardware start of incremental operation by inputting simultaneous start signal.

- 7) Incremental operation from the input point of the pulse count start signal (target position override 2)

#### Origin return sequences

A variety of origin return operations can be selected by setting of the start command and the optional operation mode bit.

<Examples of origin return sequences>

- 1) Starts feeding at constant speed and stops when the ORG signal is turned ON

- 2) Starts feeding at constant speed and stops when the LSI finishes counting specified number of EZ pulses after the ORG signal is turned ON.

- Starts feeding at high-speed decelerates when the SD signal is turned ON, and stops when the ORG signal is turned ON.

- 4) Starts feeding at high-speed, decelerates and stops when the ORG signal is turned ON.

- 5) Starts feeding at high speed, and starts decelerating when the ORG signal is turned ON. Then, stops when the LSI finishes counting specified number of EZ pulses.

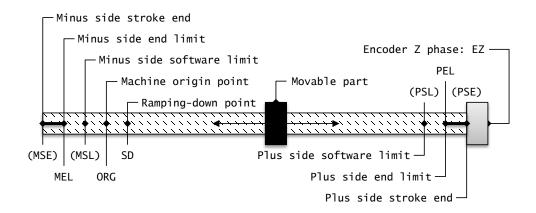

#### Mechanical input control

There are four signal input terminals for each axis as follows:

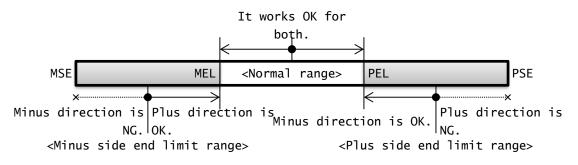

PELn The positive direction end limit signal is input.

When turning ON while moving in the positive direction, an axis will stop immediately, or decelerate and stop.

The axis will not move in the positive direction if this signal is ON when starts feeding. (The negative direction is OK.)

- 2. MELn The negative direction end limit signal is input. When turning ON while moving in the negative direction, an axis will stop immediately, or decelerate and stop. The axis will not move in the negative direction if this sigal is ON when starts feeding. (The positive direction is OK.)

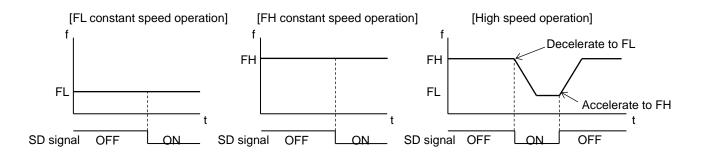

3. SDn The slow-down signal is input.

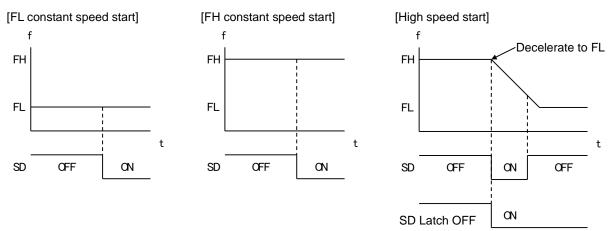

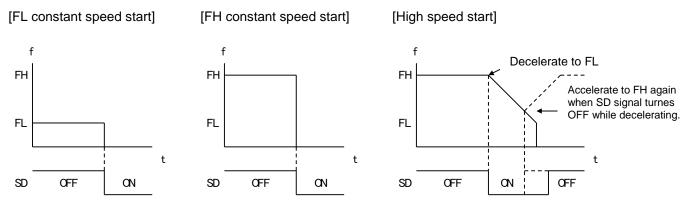

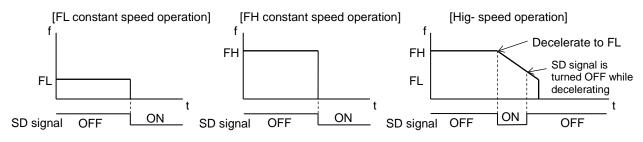

- When turning ON while moving, an axis will decelerate or decelerate and stop. If decelerate is selected, an axis will decelerate to FL speed if it is ON when starts feeding An axis will operate at FL contstant speed if this signal is ON when starts feeding. If it is set to decelerate and stop, an axis will decelerate to FL speed and then will stop.

- ORGn The origin signal is input.

When it is ON during an origin return operation, an axis will stop immidiaely, decelerate and stop, or start decelerating.

The input logic for PELn terminal and MELn terminal can be changed by changing hardware setting. The input logic for SDn terminal and ORGn terminal can be changed by changing software setting.

#### Servomotor I/F

There are three signals terminals for each axis as follows:

- 1. INPn Input a positioning complete signal that is output by a servomotor driver.

- 2. ERCn Output a deviation counter clear signal to a servomotor driver.

- 3. ALMn Input an alarm singal that is output by a servomotor driver.

When this alarm signal is ON, the axis will stop immediately or will decelerate and stop. An error interrupt is generated when the alarm signal turns ON even while the motor is stopped. If the alarm signal is ON at the start, operation will not start.

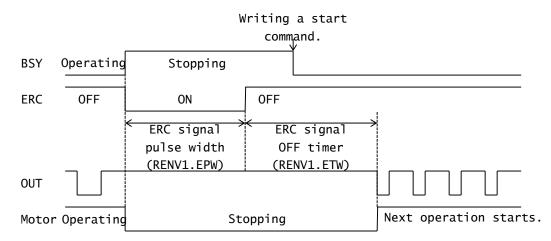

The input logic of INPn and ALMn or the output logic of ERCn can be changed by software setting. If the pulse output is selected for the deviation counter clear signal, the pulse length can be selected; (From 12 µs to 104 ms, a level output is also available.)

#### Output pulse mode

You can select from common pulse mode, 2-pulse mode and 90-degree phase difference mode. The logic can also be selected.

#### Emergency stop signal (CEMG)

When this signal is turned ON, all axes will stop immediately. If this signal is ON at start, the axis will not start.

#### Interrupt request

An INT signal (interrupt request) can be output for various factors and reasons. Interrupt factors for each axis are output from the INT terminal by a logical OR connection.

#### ♦ General-purpose input/output port

Each axis has 8-bit general-purpose input/output port. The I/O specification and logic can be changed by software settings.

#### Shared input/output port

When using the serial bus I/F, the data bus of the parallel bus I/F can be used as a 16-bit shared input/ output port.

## 2. Specification

| Item                                           | Description                                                                                            |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Number of control axes                         | PCL6115: One                                                                                           |  |  |  |  |  |

|                                                | PCL6125: Two (X and Y axes)                                                                            |  |  |  |  |  |

|                                                | PCL6145: Four (X, Y, Z, and U axes)                                                                    |  |  |  |  |  |

| Reference clock frequency (f <sub>CLK</sub> )  | Standard: 19.6608 MHz (Max. 30 MHz)                                                                    |  |  |  |  |  |

| Positioning control range                      | -2,147,483,648 to +2,147,483,647 (32-bit)                                                              |  |  |  |  |  |

| Slow-down point setting range                  | 0 to 16,777,215 (24-bit)                                                                               |  |  |  |  |  |

| Number of registers used for<br>setting speeds | Two for each axis (FL and FH)                                                                          |  |  |  |  |  |

| Speed setting step range                       | 1 to 16,383 (14-bit)                                                                                   |  |  |  |  |  |

| Speed magnification range                      | By changing the reference clock frequency, the speed range will also                                   |  |  |  |  |  |

|                                                | change with that ratio.                                                                                |  |  |  |  |  |

|                                                | 1. When the reference clock frequency = 19.6608 MHz, 0.293x to 600x.<br>(The following is an example.) |  |  |  |  |  |

|                                                | When 0.3x is selected: 0.3 to 4,914.9 pps                                                              |  |  |  |  |  |

|                                                | When 1x is selected: 1 to 16,383 pps                                                                   |  |  |  |  |  |

|                                                | When 600x is selected: 600 to 9,829,800 pps                                                            |  |  |  |  |  |

|                                                | 2. When the reference clock frequency = 30 MHz, 0.447x to 915.527x.                                    |  |  |  |  |  |

|                                                | (The following is an example.)                                                                         |  |  |  |  |  |

|                                                | When 0.5x is selected: 0.5 to 8,191.7 pps                                                              |  |  |  |  |  |

|                                                | When 1x is selected: 1 to 16,383.5 pps                                                                 |  |  |  |  |  |

|                                                | When 915.527x is selected: 915.527 to 14,999,084.5 pps                                                 |  |  |  |  |  |

| Acceleration/Deceleration                      | Linear and S-curve acceleration/deceleration. Acceleration and                                         |  |  |  |  |  |

| characteristics                                | Deceleration characteristics can be set independently.                                                 |  |  |  |  |  |

| Acceleration rate setting range                | 1 to 65,535 (16-bit)                                                                                   |  |  |  |  |  |

| Deceleration rate setting range                | 1 to 65,535 (16-bit)                                                                                   |  |  |  |  |  |

| Slow-down point automatic setting              | The automatic setting is available only when acceleration and deceleration                             |  |  |  |  |  |

| Triangular drive elimination                   | curves are symmetrical.<br>It will automatically lower the target speed, and avoid a triangular drive. |  |  |  |  |  |

| (Automatic FH correction )                     | A triangular drive is a positioning operation that an axis decelerates in the                          |  |  |  |  |  |

| (Automatic I'll conection)                     | middle of acceleration. It occurs when the feeding amount is too small.                                |  |  |  |  |  |

| Manual operation input                         | 2 signals; Manual pulser signal (PAn/PBn) and External switch signal (PDR/MDR)                         |  |  |  |  |  |

| Counters                                       | COUNTER 1 (RCUN1): Command position control counter (32-bit)                                           |  |  |  |  |  |

|                                                | COUNTER 2 (RCUN2): Mechanical position control counter (32-bit)                                        |  |  |  |  |  |

| Comparators                                    | General-purpose comparators : 32-bit x 2 circuits / axis                                               |  |  |  |  |  |

|                                                | Software limit only : 32-bit x 2 circuits / axis                                                       |  |  |  |  |  |

| CPU bus I/F                                    | 8-bit parallel bus Í/F                                                                                 |  |  |  |  |  |

|                                                | 16-bit parallel bus I/F                                                                                |  |  |  |  |  |

|                                                | Serial bus I/F ( f <sub>SCK</sub> ≦ $\frac{f_{CLK}}{1.5}$ )                                            |  |  |  |  |  |

| Interpolation functions                        | Linear interpolation: Any 2 to 4 axes                                                                  |  |  |  |  |  |

| Operating temperature range                    | -40 to +85 °C                                                                                          |  |  |  |  |  |

| Power supply                                   | 3.0 to 3.6 V                                                                                           |  |  |  |  |  |

| Package                                        | PCL6115: 80-pin QFP                                                                                    |  |  |  |  |  |

| i acitage                                      | (External dimensions 14 x 14 mm, Mold part 12 x 12 mm)                                                 |  |  |  |  |  |

|                                                | PCL6125: 128-pin QFP                                                                                   |  |  |  |  |  |

|                                                | (External dimensions 16 x 16 mm, Mold part 14 x 14 mm)                                                 |  |  |  |  |  |

|                                                | PCL6145: 176-pin QFP                                                                                   |  |  |  |  |  |

|                                                | (External dimensions 26 x 26 mm),Mold part 24 x 24 mm)                                                 |  |  |  |  |  |

|                                                |                                                                                                        |  |  |  |  |  |

#### 3. Hardware Description

#### 3-1. External dimensions

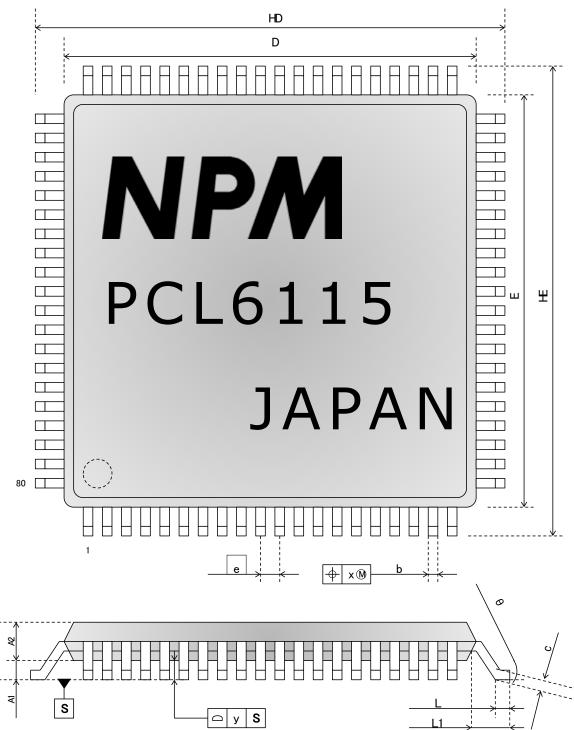

We will explain the external dimensions of each model:

1. PCL6115

Amax.

| Sumbol | Dimension in mm |       |       |  |  |  |  |

|--------|-----------------|-------|-------|--|--|--|--|

| Symbol | Min.            | Nom.  | Max.  |  |  |  |  |

| E      | 11.90           | 12.00 | 12.10 |  |  |  |  |

| D      | 11.90           | 12.00 | 12.10 |  |  |  |  |

| HE     | 13.60           | 14.00 | 14.40 |  |  |  |  |

| HD     | 13.60           | 14.00 | 14.40 |  |  |  |  |

| е      | -               | 0.50  | -     |  |  |  |  |

| b      | 0.13            | 0.20  | 0.27  |  |  |  |  |

| x      | -               | -     | 0.08  |  |  |  |  |

| A max  | -               | -     | 1.7   |  |  |  |  |

| A1     | 0.00            | 0.10  | 0.20  |  |  |  |  |

| A2     | 1.30            | 1.40  | 1.50  |  |  |  |  |

| L      | 0.30            | 0.50  | 0.75  |  |  |  |  |

| L1     | 0.80            | 1.00  | 1.20  |  |  |  |  |

| θ      | 0°              | 5°    | 10°   |  |  |  |  |

| с      | 0.09            | 0.15  | 0.20  |  |  |  |  |

| у      | -               | -     | 0.08  |  |  |  |  |

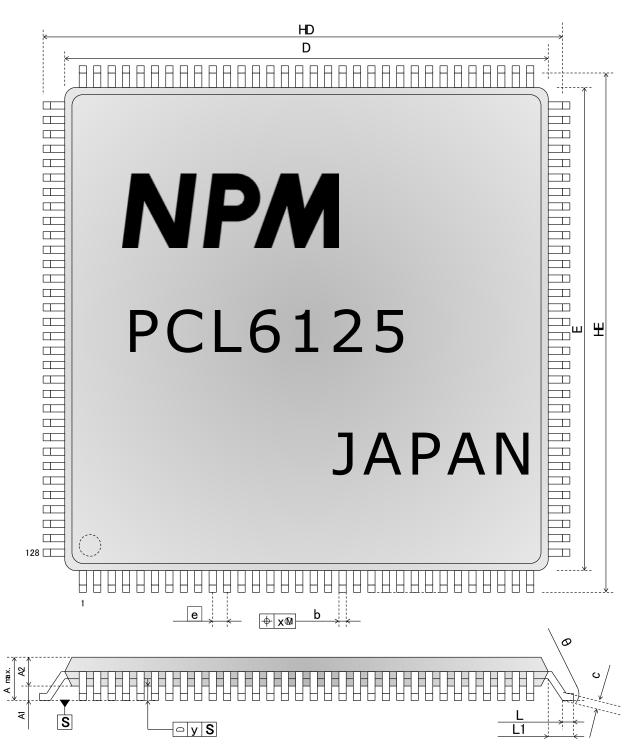

| Symbol | Dimension in mm |       |       |  |  |  |  |

|--------|-----------------|-------|-------|--|--|--|--|

| Gymbol | Min.            | Nom.  | Max.  |  |  |  |  |

| E      | 13.90           | 14.00 | 14.10 |  |  |  |  |

| D      | 13.90           | 14.00 | 14.10 |  |  |  |  |

| HE     | 15.60           | 16.00 | 16.40 |  |  |  |  |

| HD     | 15.60           | 16.00 | 16.40 |  |  |  |  |

| е      | -               | 0.40  | -     |  |  |  |  |

| b      | 0.13            | 0.18  | 0.23  |  |  |  |  |

| x      | -               | -     | 0.08  |  |  |  |  |

| A max  | -               | -     | 1.70  |  |  |  |  |

| A1     | 0.00            | 0.10  | 0.20  |  |  |  |  |

| A2     | 1.30            | 1.40  | 1.50  |  |  |  |  |

| L      | 0.30            | 0.50  | 0.75  |  |  |  |  |

| L1     | 0.80            | 1.00  | 1.20  |  |  |  |  |

| θ      | 0°              | 5°    | 10°   |  |  |  |  |

| С      | 0.09            | 0.15  | 0.20  |  |  |  |  |

| У      | -               | -     | 0.08  |  |  |  |  |

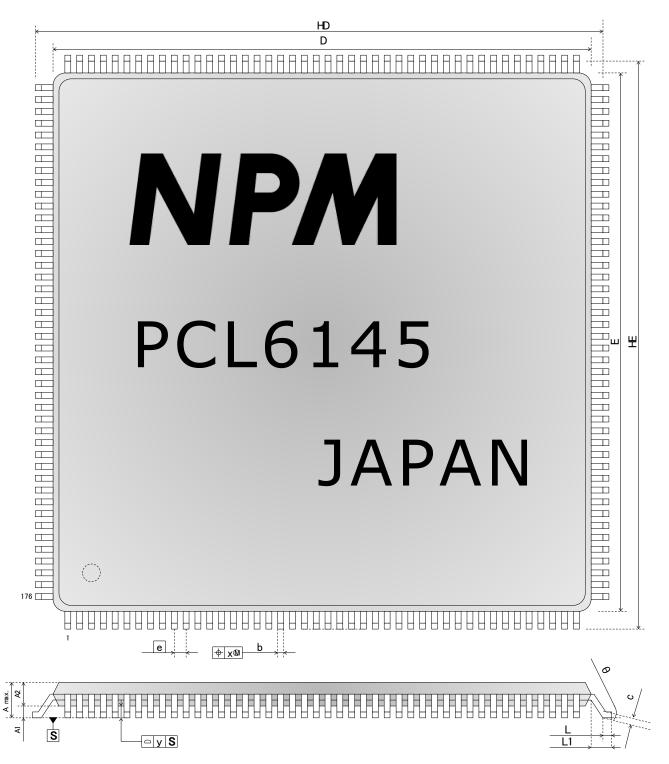

| Cumb ol | Dimension in mm |       |       |  |  |  |  |

|---------|-----------------|-------|-------|--|--|--|--|

| Symbol  | Min.            | Nom.  | Max.  |  |  |  |  |

| E       | 23.90           | 24.00 | 24.10 |  |  |  |  |

| D       | 23.90           | 24.00 | 24.10 |  |  |  |  |

| HE      | 25.60           | 26.00 | 26.40 |  |  |  |  |

| HD      | 25.60           | 26.00 | 26.40 |  |  |  |  |

| е       | -               | 0.50  | -     |  |  |  |  |

| b       | 0.17            | 0.22  | 0.27  |  |  |  |  |

| x       | -               | -     | 0.08  |  |  |  |  |

| A max   | -               | -     | 1.70  |  |  |  |  |

| A1      | 0.00            | 0.10  | 0.20  |  |  |  |  |

| A2      | 1.30            | 1.40  | 1.50  |  |  |  |  |

| L       | 0.30            | 0.50  | 0.75  |  |  |  |  |

| L1      | 0.80            | 1.00  | 1.20  |  |  |  |  |

| θ       | 0°              | 5°    | 10°   |  |  |  |  |

| С       | 0.09            | 0.15  | 0.20  |  |  |  |  |

| У       | -               | -     | 0.08  |  |  |  |  |

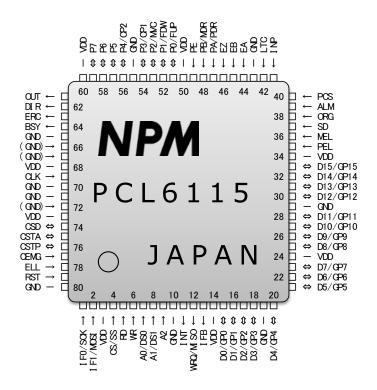

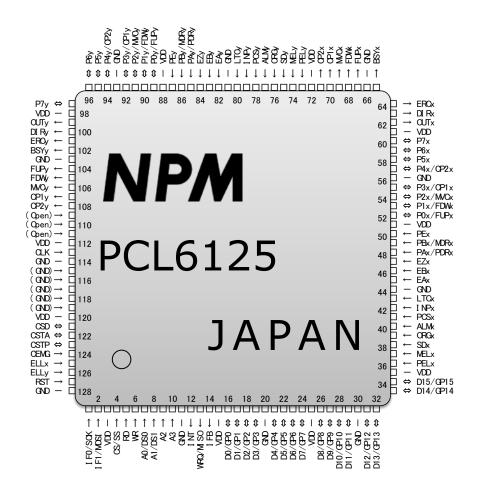

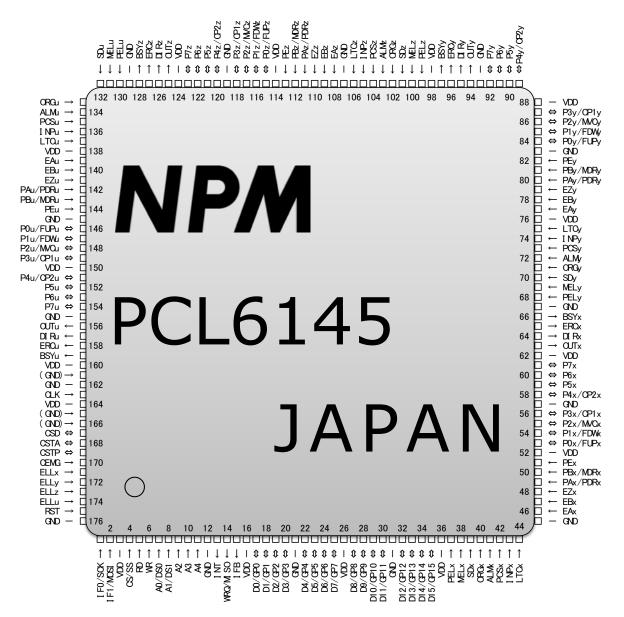

#### 3-2. Terminal Assignment Diagrams

The following shows the terminal assignments of each LSI:

#### 1. PCL6115

Note: The lower left of the model name marking is pin number 1.

2. PCL6125

Note: The lower left of the model name marking is pin number 1.

Note: The lower left of the model name marking is pin number 1.

#### 3-3. Terminal List

Note:

- 1. "Direction" column indicates the signal direction; "I" means input, "O" means output, and "B" means bi-directional.

- 2. "Logic" column indicates the signal logic; "P" means positive logic, N" means negative logic. "#" means changeable with software. "%" means set by hardware

- "Handling" column describes how to deal with terminals when they are not used. Some terminals need to be processed when they are used.

"OP" means to leave open, "PU" means to pull up, "PU (PD)" means to pull-up or to pull-down, "+V" means to connect directly to VDD or to pull up, and "GN" means to connect directly to GND or to pull-down. A resistance value of 5k to 10k ohm is recommended.

- 4. 0 V to +5 V level can be input to input terminals of all signals.

- 5. The output terminals of all signals can be pulled up to +5 V. However, equal to or more than VDD cannot be output. (Equal to or more than 5k to 10k ohm resistant value is recommended.)

| Terminal No. | Signal name | Direction | Logic | Handling | Description                                       |

|--------------|-------------|-----------|-------|----------|---------------------------------------------------|

| 1            | IF0/SCK     | I         | -     | -        | Parallel bus I/F: Sets CPU bus I/F mode.          |

|              |             |           |       |          | Serial bus I/F: Inputs serial clock signal.       |

| 2            | IF1/MOSI    | I         | -     | -        | Parallel bus I/F: Sets CPU bus I/F mode.          |

|              |             |           |       |          | Serial bus I/F: Input output data from CPU.       |

| 3            | VDD         | -         | -     | -        | Power supply terminal.                            |

|              |             |           |       |          | Connect to 3.3 V.                                 |

| 4            | CS/SS       | I         | Ν     | -        | Parallel bus I/F: Inputs chip select signal.      |

|              |             |           |       |          | Serial bus I/F: Inputs slave select signal.       |

| 5            | RD          | I         | Ν     | -        | Parallel bus I/F: Inputs read out signal.         |

|              |             |           |       |          | Serial bus I/F: Connects to GND.                  |

| 6            | WR          | I         | Ν     |          | Parallel bus I/F: Inputs write signal.            |

|              |             |           |       |          | Serial bus I/F: Connects to GND.                  |

| 7            | A0 / DS0    | I         | Р     | -        | Parallel bus I/F: Inputs address signal.          |

| 8            | A1 / DS1    |           |       |          | Serial bus I/F: Sets device select number.        |

| 9            | A2          | I         | Р     | PU       | Parallel bus I/F: Inputs address signal.          |

|              |             |           |       | (PD)     | Serial bus I/F: Sets device select number.        |

| 10           | GND         | -         | -     | -        | Power supply terminal.                            |

|              |             |           |       |          | Connects to GND.                                  |

| 11           | INT         | 0         | Ν     | OP       | Outputs interrupt request signal.                 |

|              |             |           |       |          | See "7-13. Interrupt (INT) function" for details. |

#### 3-3-1. PCL6115

| Terminal No. | Signal name | Direction | Logic | Handling | Description                                                      |

|--------------|-------------|-----------|-------|----------|------------------------------------------------------------------|

| 12           | WRQ/MISO    | 0         | Ν     | OP       | Parallel bus I/F: Outputs wait request signal.                   |

|              |             |           |       |          | Serial bus I/F: Outputs input data to CPU.                       |

| 13           | IFB         | 0         | Ν     | OP       | Parallel bus I/F: Outputs interface operation signal.            |

|              |             |           |       |          | Serial bus I/F: Leave it open.                                   |

| 14           | VDD         |           |       |          | Power supply terminal.                                           |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| 15           | D0/GP0      | В         | Р     | PU       | Parallel bus I/F: Connect data bus; Bit 0 to Bit 3.              |

| 16           | D1/GP1      |           |       | (PD)     | Serial bus I/F: Become shared input/output ports; GP0 to GP3     |

| 17           | D2/GP2      |           |       |          | terminals.                                                       |

| 18           | D3/GP3      |           |       |          |                                                                  |

| 19           | GND         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to GND.                                                 |

| 20           | D4/GP4      | В         | Р     | PU       | Parallel bus I/F: Connect data bus; Bit 4 to Bit 7.              |

| 21           | D5/GP5      |           |       | (PD)     | Serial bus I/F: Become shared input/output ports; GP4 to GP7     |

| 22           | D6/GP6      |           |       |          | terminals.                                                       |

| 23           | D7/GP7      |           |       |          |                                                                  |

| 24           | VDD         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| 25           | D8/GP8      | В         | Р     | PU       | Parallel bus I/F: Connect 6-bit data bus; Bit 8 to Bit 11.       |

| 26           | D9/GP9      |           |       | (PD)     | 8-bit data bus needs to be pulled-up or pulled-down.             |

| 27           | D10/GP10    |           |       |          | Serial bus I/F: Become shared input/output ports; GP8 to GP11    |

| 28           | D11/GP11    |           |       |          | terminals.                                                       |

| 29           | GND         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to GND.                                                 |

| 30           | D12/GP12    | В         | Р     | PU       | Parallel bus I/F: Connect the 16-bit data bus; Bit 12 to Bit 15. |

| 31           | D13/GP13    |           |       | (PD)     | 8-bit data bus needs to be pulled up or pulled down.             |

| 32           | D14/GP14    |           |       |          | Serial bus I/F: Become shared input/output ports; GP12 to        |

| 33           | D15/GP15    |           |       |          | GP15 terminals.                                                  |

| 34           | VDD         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| 35           | PEL         | I         | N%    | +V       | Inputs end limit signal in the positive direction.               |

|              |             |           |       |          | See "7-4-1. End limit signal (PELn, MELn)" for details.          |

| 36           | MEL         | I         | N%    | +V       | Inputs end limit signal in the negative direction.               |

|              |             |           |       |          | See "7-4-1. End limit signal (PELn, MELn)" for details.          |

| Terminal No. | Signal name | Direction | Logic | Handling | Description                                                      |

|--------------|-------------|-----------|-------|----------|------------------------------------------------------------------|

| 37           | SD          | I         | N#    | +V       | Inputs slow-down signal.                                         |

|              |             |           |       |          | See "7-4-2. Slow-down signal (SDn)" for details.                 |

| 38           | ORG         | I         | N#    | +V       | Inputs origin position signal.                                   |

|              |             |           |       |          | See " <u>7-4-3. Origin signal (ORGn), Encoder Z-phase signal</u> |

|              |             |           |       |          | ( <u>EZn)</u> " for details.                                     |

| 39           | ALM         | I         | N#    | +V       | Inputs alarm signal input from a servomotor driver.              |

|              |             |           |       |          | See "7-5-3. Alarm signals (ALMn)" for details.                   |

| 40           | PCS         | I         | N#    | GN       | Inputs pulse count start signal or own-axis start signal.        |

|              |             |           |       |          | See "7-2-2. Target position override 2 (PCSn)" or "7-6-2.        |

|              |             |           |       |          | Own-axis start signal (PCSn)" for details.                       |

| 41           | INP         | I         | N#    | GN       | Inputs positioning complete signal from a servomotor driver.     |

|              |             |           |       |          | (In-position signal).                                            |

|              |             |           |       |          | See " <u>7-5-1. INP signal</u> " for details.                    |

| 42           | LTC         | I         | N#    | GN       | Inputs counter latch signal.                                     |

|              |             |           |       |          | See "7-10-2. Latch and reset (LTCn)" for details.                |

| 43           | GND         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to GND.                                                 |

| 44           | EA          | I         | -     | GN       | Inputs phase A signals from an encoder.                          |

|              |             |           |       |          | See "7-10-1. Counter type and input specification" for details.  |

| 45           | EB          | I         | -     | GN       | Inputs phase B signals from an encoder.                          |

|              |             |           |       |          | See "7-10-1. Counter type and input specification" for details.  |

| 46           | EZ          | I         | N#    | GN       | Inputs phase Z signals from an encoder.                          |

|              |             |           |       |          | See "7-4-3. Origin positon signal (ORGn), encoder Z-phase        |

|              |             |           |       |          | signal (EZn)" for details.                                       |

| 47           | PA/PDR      | I         | -     | GN       | Connects to phase A of a manual pulser or to the positive        |

|              |             |           |       |          | direction of an external switch.                                 |

|              |             |           |       |          | See "5-3. Manual pulser operation" or "5-4. Switch operation"    |

|              |             |           |       |          | for details.                                                     |

| 48           | PB/MDR      | I         | -     | GN       | Connects to phase B of a manual pulser or to the negative        |

|              |             |           |       |          | direction of an external switch.                                 |

|              |             |           |       |          | See "5-3. Manual pulser operation" or "5-4. Switch operation"    |

|              |             |           |       |          | for details.                                                     |

| 49           | PE          | I         | Ν     | GN       | Inputs manual pulser signals or external switch enable signal.   |

|              |             |           |       |          | L level (GN): Controllable by PA/PDR terminals and PB/MDR        |

|              |             |           |       |          | terminals.                                                       |

|              |             |           |       |          | H level (+V): Uncontrollable by PA/PDR terminals and             |

|              |             |           |       |          | PB/MDR terminals.                                                |

| 50           | VDD         | -         | -     | -        | Power supply terminal.                                           |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| Terminal No. | Signal name | Direction | Logic | Handling                              | Description                                                                                          |

|--------------|-------------|-----------|-------|---------------------------------------|------------------------------------------------------------------------------------------------------|

| 51           | P0/FUP      | В         | -     | PU                                    | P0 terminal used for general-purpose input/output port or                                            |

|              |             |           |       | (PD)                                  | output terminal for on-going acceleration signal.                                                    |

|              |             |           |       |                                       | See "4-4-4-3. RENV2: Environment setting 2 register" for                                             |

|              |             |           |       |                                       | details.                                                                                             |

| 52           | P1/FDW      | В         | -     | PU                                    | P1 terminal used for general-purpose input/output port or                                            |

|              |             |           |       | (PD)                                  | output terminal for on-going deceleration signal.                                                    |

|              |             |           |       |                                       | See " <u>4-4-4-3. RENV2: Environment setting 2 register</u> " for                                    |

|              |             |           |       |                                       | details.                                                                                             |

| 53           | P2/MVC      | В         | -     | PU                                    | P2 terminal used for general-purpose input/output port or                                            |

|              |             |           |       | (PD)                                  | output terminal for on-going constant speed operation signal.                                        |

|              |             |           |       |                                       | See " <u>4-4-4-3. RENV2: Environment setting 2 register</u> " for                                    |

| - 1          | D0/0D/      |           |       |                                       | details.                                                                                             |

| 54           | P3/CP1      | В         | -     | PU                                    | P3 terminal used for general-purpose input/output port of                                            |

|              |             |           |       | (PD)                                  | output terminal for signal that indicates the condition of                                           |

|              |             |           |       |                                       | comparator 1 is met. See " <u>4-4-4-3. RENV2: Environment</u>                                        |

| FF           | GND         |           |       |                                       | setting 2 register" for details.                                                                     |

| 55<br>56     | P4/CP2      | B         | -     | -<br>PU                               | Power supply terminal. Connects to GND.<br>P4 terminal used for general purpose input/output port or |

| 50           | F4/CF2      | D         | -     | PD)                                   | output terminal for signal that indicates the condition of                                           |

|              |             |           |       | (FD)                                  | comparator 2 is met. See "4-4-4-3. RENV2: Environment                                                |

|              |             |           |       |                                       | setting 2 register" for details.                                                                     |

| 57           | P5          | В         | _     | PU                                    | P5 terminal used for general purpose input/output port.                                              |

| 01           | 10          |           |       | (PD)                                  | See "4-4-4-3. RENV2: Environment setting 2 register" for                                             |

|              |             |           |       | ()                                    | details.                                                                                             |

| 58           | P6          | В         | -     | PU                                    | P6 terminal used for general purpose input/output port.                                              |

|              |             |           |       | (PD)                                  | See "4-4-4-3. RENV2: Environment setting 2 register" for                                             |

|              |             |           |       | , , , , , , , , , , , , , , , , , , , | details.                                                                                             |

| 59           | P7          | В         | -     | PU                                    | P7 terminal used for general purpose input/output port                                               |

|              |             |           |       | (PD)                                  | See "4-4-4-3. RENV2: Environment setting 2 register" for                                             |

|              |             |           |       |                                       | details.                                                                                             |

| 60           | VDD         | -         | -     | -                                     | Power supply terminal. Connects to 3.3 V.                                                            |

| 61           | OUT         | 0         | N#    | OP                                    | Outputs command pulse to a motor driver.                                                             |

|              |             |           |       |                                       | See "7-3-1. Output pulse mode (OUTn, DIRn)" for details.                                             |

| 62           | DIR         | 0         | N#    | OP                                    | Outputs command pulse to a motor driver.                                                             |

|              |             |           |       |                                       | See "7-3-1. Output pulse mode (OUTn, DIRn)" for details.                                             |

| 63           | ERC         | 0         | N#    | OP                                    | Outputs deviation counter clear signal to a servomotor driver.                                       |

|              |             |           |       |                                       | See "7-5-2. Deviation counter clear signal (ERCn)" for details.                                      |

| 64           | BSY         | 0         | Ν     | OP                                    | Outputs signal to indicate that an operation is in progress.                                         |

|              |             |           |       |                                       | It becomes L level during operation.                                                                 |

| 65           | GND         | -         | -     | -                                     | Power supply terminal. Connects to GND.                                                              |

| 66           | (GND)       | I         | -     | GN                                    | Input terminal for shipping inspection. Connects to GND.                                             |

| 67           |             |           |       |                                       |                                                                                                      |

| 68           | VDD         | -         | -     | -                                     | Power supply terminal. Connects to 3.3 V.                                                            |

| Terminal No. | Signal name | Direction | Logic | Handling | Description                                                                                                                        |

|--------------|-------------|-----------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 69           | CLK         | I         | -     | -        | Inputs reference clock (CLK) signal.<br>Standard frequency is 19.6608 MHz.                                                         |

| 70           | GND         | -         | -     | -        | Power supply terminal<br>Connects to GND.                                                                                          |

| 71           | GND         | -         | -     | -        | Power supply terminal<br>Connects to GND.                                                                                          |

| 72           | (GND)       | Ι         | -     | GN       | Input terminal for shipping inspection.<br>Connects to GND.                                                                        |

| 73           | VDD         | -         | -     | -        | Power supply terminal<br>Connects to 3.3 V.                                                                                        |

| 74           | CSD         | В         | Ν     | PU       | Inputs/Outputs simultaneous deceleration signal.<br>See " <u>7-7-1. Simultaneous deceleration signal (CSD)</u> " for details.      |

| 75           | CSTA        | В         | Ν     | PU       | Inputs/Outputs simultaneous start signal.<br>See " <u>7-6-1. Simultaneous start signal (CSTA)</u> " for details.                   |

| 76           | CSTP        | В         | Ν     | PU       | Inputs/Outputs simultaneous stop signal.<br>See " <u>7-8-1. Simultaneous stop signal (CSTP)</u> " for details.                     |

| 77           | CEMG        | I         | Ν     | +V       | Inputs emergency stop signal.<br>See " <u>7-9-1. Emergency stop signal (CEMG)</u> " for details.                                   |

| 78           | ELL         | I         | -     | -        | Selects the input logic of end limit signal.<br>L level (GN) : Input logic is positive.<br>H level (+V) : Input logic is negative. |

| 79           | RST         | I         | N     | -        | Inputs reset signal.<br>See " <u>7-1. Reset</u> " for details.                                                                     |

| 80           | GND         | -         | -     | -        | Power supply terminal<br>Connects to GND.                                                                                          |

#### 3-3-2. PCL6125

| Terminal No.         | Signal name                          | Direction | Logic | Handling   | Description                                                                                                                        |

|----------------------|--------------------------------------|-----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | IF0/SCK                              | I         | -     | -          | Parallel bus I/F: Sets CPU bus I/F mode.<br>Serial bus I/F: Input serial clock signal.                                             |

| 2                    | IF1/MOSI                             | I         | -     | -          | Parallel bus I/F: Sets CPU bus I/F mode.<br>Serial bus I/F: Input output data from CPU.                                            |

| 3                    | VDD                                  | -         | -     | -          | Power supply terminal<br>Connects to 3.3 V.                                                                                        |

| 4                    | CS/SS                                | Ι         | Ν     | -          | Parallel bus I/F: Inputs chip select signal.<br>Serial bus I/F: Inputs slave select signal.                                        |

| 5                    | RD                                   | I         | Ν     | -          | Parallel bus I/F: Inputs read out signal.<br>Serial bus I/F: Connects to GND.                                                      |

| 6                    | <u>WR</u>                            | I         | Ν     | -          | Parallel bus I/F: Inputs write signal.<br>Serial bus I/F: Connects to GND.                                                         |

| 7<br>8               | A0 / DS0<br>A1 / DS1                 | Ι         | Ρ     | -          | Parallel bus I/F: Inputs address signal.<br>Serial bus I/F: Sets device select number.                                             |

| 9<br>10              | A2<br>A3                             | I         | Р     | PU<br>(PD) | Parallel bus I/F: Inputs address signal.<br>Serial bus I/F: To be pulled up or pulled down.                                        |

| 11                   | GND                                  | -         | -     | -          | Power supply terminal.<br>Connects to GND.                                                                                         |

| 12                   | INT                                  | 0         | Ν     | OP         | Outputs interrupt request signal.<br>See " <u>7-13. Interrupt (INT) function</u> " for details.                                    |

| 13                   | WRQ/MISO                             | 0         | Ν     | OP         | Parallel bus I/F: Outputs wait request signal.<br>Serial bus I/F: Outputs input data to CPU.                                       |

| 14                   | IFB                                  | 0         | Ν     | OP         | Parallel bus I/F: Outputs interface operation signal.<br>Serial bus I/F: Leave it open.                                            |

| 15                   | VDD                                  | -         | -     | -          | Power supply terminal.<br>Connects to 3.3 V.                                                                                       |

| 16<br>17<br>18<br>19 | D0/GP0<br>D1/GP1<br>D2/GP2<br>D3/GP3 | В         | Ρ     | PU<br>(PD) | Parallel bus I/F: Connects data bus; Bit 0 to Bit 3.<br>Serial bus I/F: Become shared input/output ports; GP0 to GP3<br>terminals. |

| 20                   | GND                                  | -         | -     | -          | Power supply terminal<br>Connects to GND.                                                                                          |

| Terminal No. | Signal name | Direction | Logic | Handling | Description                                                      |

|--------------|-------------|-----------|-------|----------|------------------------------------------------------------------|

| 21           | D4/GP4      | В         | Р     | PU       | Parallel bus I/F: Connects data bus; Bit 4 to Bit 7.             |

| 22           | D5/GP5      |           |       | (PD)     | Serial bus I/F: Becomes shared input/output ports; GP4 to GP7    |

| 23           | D6/GP6      |           |       |          | terminals.                                                       |

| 24           | D7/GP7      |           |       |          |                                                                  |

| 25           | VDD         | -         | -     | -        | Power supply terminal                                            |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| 26           | D8/GP8      | В         | Р     | PU       | Parallel bus I/F: Connect 16-bit data bus; Bit 8 to Bit 11.      |

| 27           | D9/GP9      |           |       | (PD)     | 8-bit data bus needs to be pulled up or pulled down.             |

| 28           | D10/GP10    |           |       |          | Serial bus I/F: Becomes shared input/output ports; GP8 to        |

| 29           | D11/GP11    |           |       |          | GP11 terminals.                                                  |

| 30           | GND         | -         | -     | -        | Power supply terminal                                            |

|              |             |           |       |          | Connects to GND.                                                 |

| 31           | D12/GP12    | В         | Р     | PU       | Parallel bus I/F: Connect 16-bit data bus; Bit 12 to Bit 15.     |

| 32           | D13/GP13    |           |       | (PD)     | 8-bit data bus needs to be pulled up or pulled down.             |

| 33           | D14/GP14    |           |       |          | Serial bus I/F: Becomes shared input/output ports; GP12 to       |

| 34           | D15/GP15    |           |       |          | GP15 terminals.                                                  |

| 35           | VDD         | -         | -     | -        | Power supply terminal                                            |

|              |             |           |       |          | Connects to 3.3 V.                                               |

| 36           | PELx        | I         | N%    | +V       | Inputs end limit signal in the positive direction.               |

|              |             |           |       |          | See "7-4-1. End limit signal (PELn, MELn)" for details.          |

| 07           |             |           | N10/  |          |                                                                  |

| 37           | MELx        | I         | N%    | +V       | Inputs end limit signal in the negative direction.               |

|              |             |           |       |          | See " <u>7-4-1. End limit signal (PELn, MELn)</u> " for details. |

| 38           | SDx         | I         | N#    | +V       | Input slow-down signal.                                          |

|              |             |           |       |          | See " <u>7-4-2. Slow-down signal (SDn)</u> " for details.        |

| 39           | ORGx        | I         | N#    | +V       | Inputs origin position signal.                                   |

|              |             |           |       |          | See "7-4-3. Origin position signal (ORGn) and Encoder            |

|              |             |           |       |          | Z-phase signal (EZn)" for details.                               |

| 40           | ALMx        | I         | N#    | +V       | Inputs alarm signal input from a servomotor driver.              |

|              |             |           |       |          | See <u>"7-5-3. Alarm signal (ALMn)</u> " for details.            |

| 41           | PCSx        | I         | N#    | GN       | Inputs pulse count start signal or own-axis start signal.        |

|              |             |           |       |          | See "7-2-2. Target position override 2 (PCSn)" or "7-6-2.        |

|              |             |           |       |          | Own-axis start signal (PCSn)" for details.                       |

| 42           | INPx        | I         | N#    | GN       | Inputs positioning complete signal from a servo driver.          |

|              |             |           |       |          | (In-position signal).                                            |

|              |             |           |       |          | See "7-5-1. Positioning complete signal (INPn)" for details.     |

| Terminal No. | Signal name | Direction | Logic | Handling   | Description                                                              |

|--------------|-------------|-----------|-------|------------|--------------------------------------------------------------------------|

| 43           | LTCx        | I         | N#    | GN         | Inputs counter latch signals.                                            |

|              |             |           |       |            | See "7-10-2. Latch and clear (LTCn)" for details.                        |

| 44           | GND         | -         | -     | -          | Power supply terminal                                                    |

|              |             |           |       |            | Connects to GND.                                                         |

| 45           | EAx         | I         | -     | GN         | Inputs phase A signals from an encoder                                   |

|              |             |           |       |            | See " <u>7-10-1. Counter type and input specification</u> " for details. |

| 46           | EBx         | I         | -     | GN         | Inputs phase B signals from an encoder                                   |

|              |             |           |       |            | See " <u>7-10-1. Counter type and input specification</u> " for details. |

| 47           | EZx         | I         | N#    | GN         | Inputs the phase Z signals from an encoder.                              |

|              |             |           |       |            | See "7-4-3. Origin positon signals (ORGn), encoder Z-phase               |

|              |             |           |       |            | <u>signals (EZn)</u> " for details.                                      |

| 48           | PAx/PDRx    | I         | -     | GN         | Connects to phase A of a manual pulser or the positive                   |

|              |             |           |       |            | direction of an external switch. See <u>"5-3. Manual pulser</u>          |

|              |             |           |       |            | operation" or " <u>5-4. Switch operation</u> " for details.              |

| 49           | PBx/MDRx    | I         | -     | GN         | Connects to phase B of a manual pulser or the negative                   |

|              |             |           |       |            | direction of an external switch. See " <u>5-3. Manual pulser</u>         |

|              |             |           |       |            | operation" or " <u>5-4. Switch operation</u> for details.                |

| 50           | PEx         | I         | Ν     | GN         | Inputs manual pulser signal or external switch enable signal.            |

|              |             |           |       |            | L level (GN): Controllable by PAx/PDRx terminals and                     |

|              |             |           |       |            | PBx/MDRx terminals. H level (+V): Uncontrollable by                      |

|              |             |           |       |            | PAx/PDRx terminals and PBx/MDRx terminals.                               |

| 51           | VDD         | -         | -     | -          | Power supply terminal                                                    |

|              |             | _         |       |            | Connects to 3.3 V.                                                       |

| 52           | P0x/FUPx    | В         | -     | PU         | P0 terminal used for general purpose input/output port or                |

|              |             |           |       | (PD)       | output terminal for on-going acceleration signal.                        |

|              |             |           |       |            | See " <u>4-4-4-3. RENV2: Environment setting 2 register</u> " for        |

| 50           | P1x/FDWx    | Р         |       |            | details.<br>P1 terminal used for general purpose input/output port or    |

| 53           | FIX/FDVVX   | В         | -     | PU<br>(PD) | output terminal for on-going deceleration signal.                        |

|              |             |           |       | (FD)       | See "4-4-4-3. RENV2: Environment setting 2 register" for                 |

|              |             |           |       |            | details.                                                                 |

| 54           | P2x/MVCx    | В         | -     | PU         | P2 terminal used for general purpose input/output port or                |

| 01           |             |           |       | (PD)       | output terminal for on-going constant speed operation signal.            |

|              |             |           |       | (          | See "4-4-4-3. RENV2: Environment setting 2 register" for                 |

|              |             |           |       |            | details.                                                                 |

| 55           | P3x/CP1x    | В         | -     | PU         | P3 terminal used for general purpose input/output port or                |

|              |             |           |       | (PD)       | output terminal for signal that indicates the condition of               |

|              |             |           |       | , í        | comparator 1 is met. See "4-4-4-3. RENV2: Environment                    |

|              |             |           |       |            | setting 2 register" for details.                                         |

| 56           | GND         | -         | -     | -          | Power supply terminal                                                    |

|              |             |           |       |            | Connects to GND.                                                         |

| 57           | P4x/CP2x    | В         | -     | PU         | P4 terminal used for general purpose input/output port or                |

|              |             |           |       | (PD)       | output terminal for signal that indicates the condition of               |

|              |             |           |       |            | comparator 2 is met. See " <u>4-4-4-3. RENV2: Environment</u>            |

|              |             |           |       |            | setting 2 register" for details.                                         |

| Terminal No. | Signal name | Direction | Logic        | Handling   | Description                                                                                                        |

|--------------|-------------|-----------|--------------|------------|--------------------------------------------------------------------------------------------------------------------|

| 58           | P5x         | В         | -            | PU<br>(PD) | P5 terminal used for general purpose input/output port<br>See "4-4-4-3. RENV2: Environment setting 2 register" for |

|              |             |           |              | (1 D)      | details.                                                                                                           |

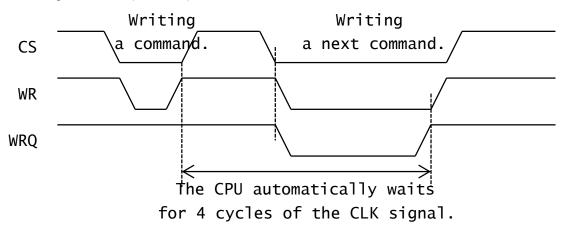

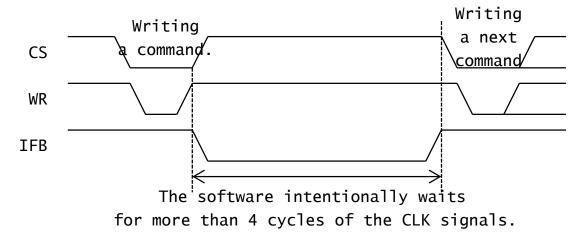

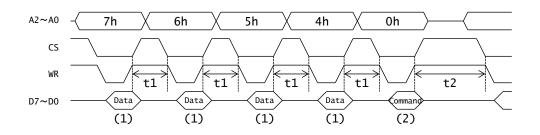

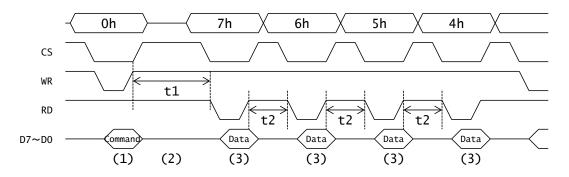

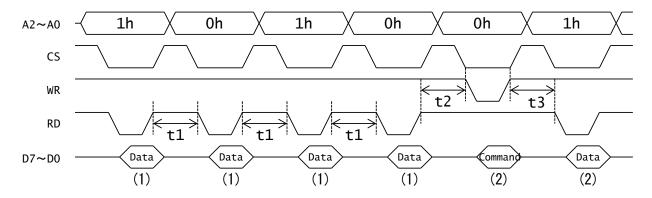

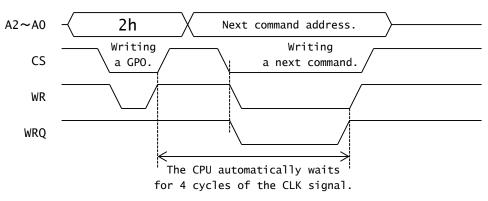

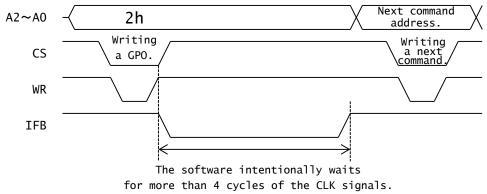

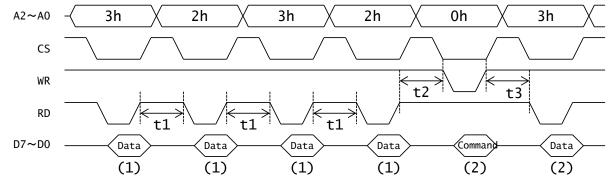

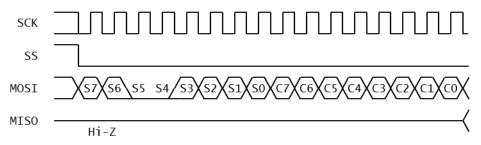

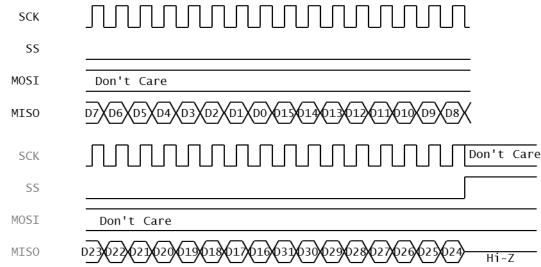

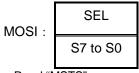

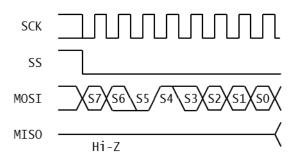

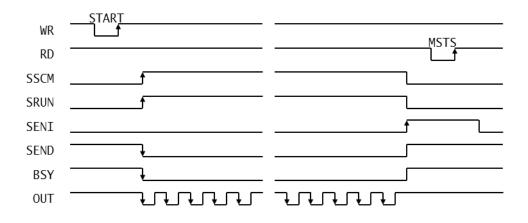

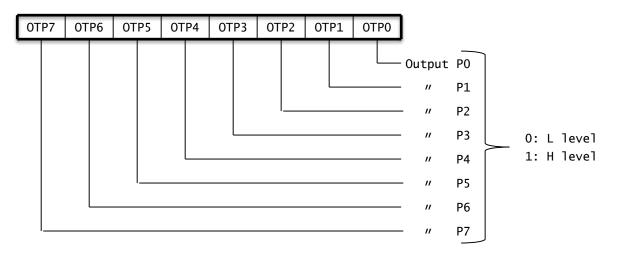

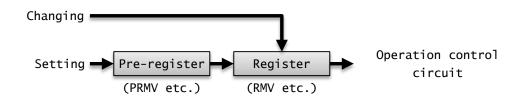

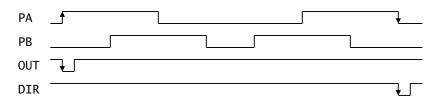

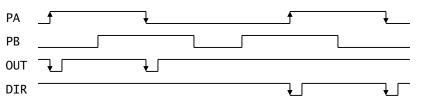

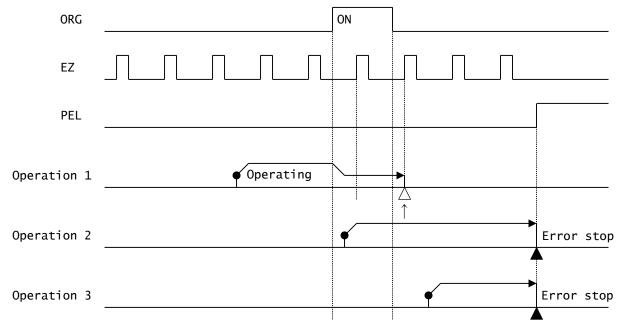

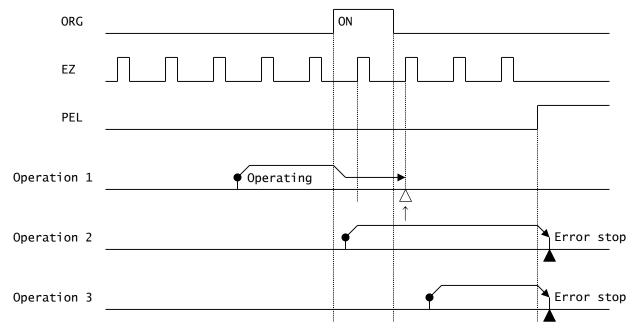

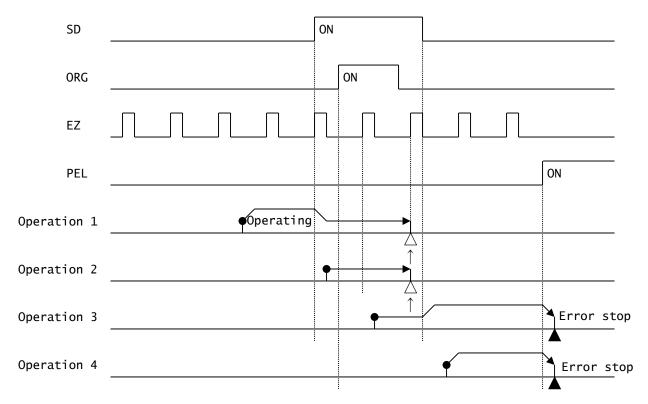

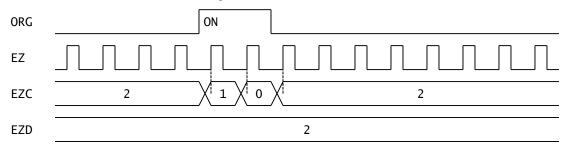

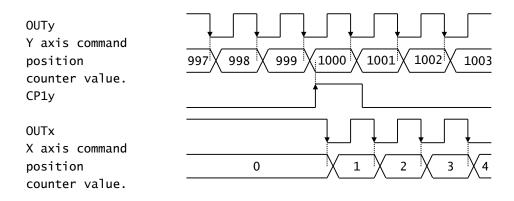

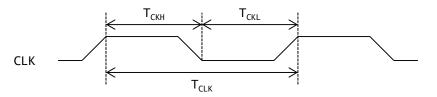

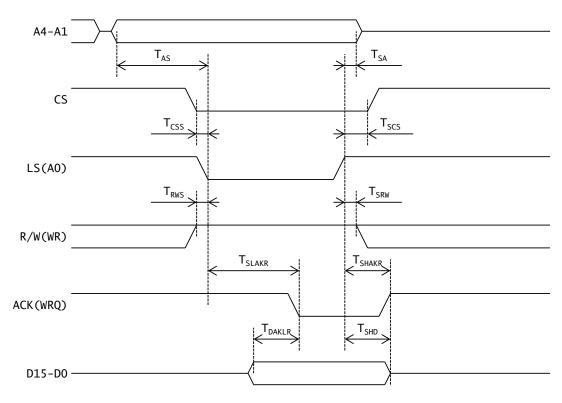

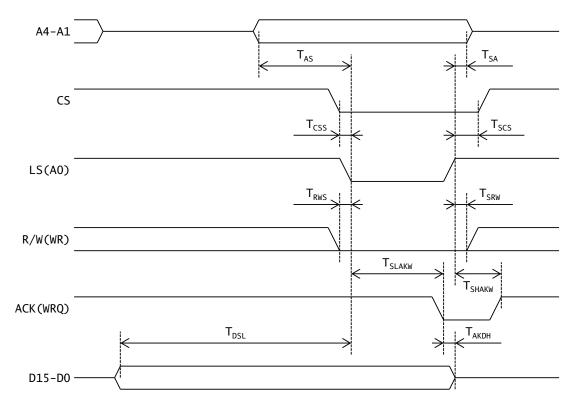

| 59           | P6x         | В         | -            | PU         | P6 terminal used for general purpose input/output port                                                             |